انجام پروژه Verilog، ارائه خدمات شبیه سازی با Verilog توسط صدها کارشناس حرفه ای متلب پروژه با قیمت مناسب و کیفیت عالی انجام میشود، متلب پروژه با بهره گیری از اساتید ممتاز این تضمین را به شما میدهد که مطمئن ترین سایت را برای پروژه خود انتخاب کرده اید. برای سفارش انجام پروژه های دانشجویی Verilog میتوانید با شماره 09962031191 در تماس باشید و یا برای اطلاع از هزینه پروژه های وریلاگ از طریق واتساپ و یا به آیدی تلگرام matlabprozhe2@ پیام دهید.

در مواقع فراوانی شاهد هستیم کاربران در پروژه های Verilog خود دچار مشکل هستند و به دنبال یک مکان مطمئن برای سفارش خود هستند.

متلب پروژه با کسب کارنامه ای درخشان و تجربه 10 ساله آمادگی دارد انجام پروژه های Verilog را در تمامی مقاطع بر عهده گرفته و با کمترین قیمت تحویل شما دهد.

دقت داشته باشید هزینه پروژه Verilog در متلب پروژه کاملا عادلانه است و از میان مجموعه پیشنهادات کمترین قیمت به صورت مناقصه ای خدمت مشتریان اعلام میشود.

Verilog چیست؟

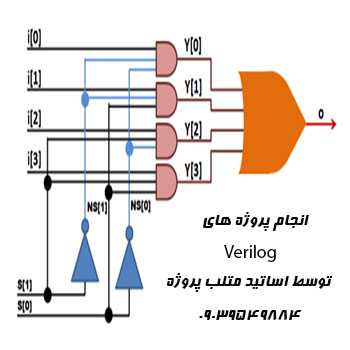

Verilog یا وریلاگ یک زبان برنامه نویسی قدرتمند کامپیوتر در حوزه توصیف سخت افزار می باشد که کاربرد اصلی آن در طراحی سیستم های دیجیتال می باشد. انجام پروژه های Verilog نقش مهمی در توصیف سخت افزار، شبیه سازی سیستمهای دیجیتال و بررسی رفتار مدارهای الکترونیکی دارد. هدف از طراحی Verilog ارائه محیط برنامه نویسی جامع جهت راه اندازی مدارهای منطقی و مدلسازی سیستم های دیجیتال می باشد. Verilog همچنین توانایی مدل سازی چند سطحی از الگوریتم ها تا سطح گیت، شبیهسازی رفتار مدارها قبل از ساخت و طراحی های مدار مجتمع را نیز دارد. Verilog دارای قابلیت های فراوانی از جمله توصیف جریان داده ، برنامه نویسی سخت افزارها، بررسی رفتار مدار دیجیتال ، مدلسازی انواع سیستم های دیجیتال و توصیف سخت افزار را دارا می باشد. یکی از ویژگی های بسیار مهم وریلاگ طراحی انواع سیستم های دیجیتالی و توصیف کامل عملکرد این سیستم ها می باشد که اجازه تجزیه و تحلیل خودکار و شبیهسازی یک مدار الکترونیکی را میدهد وریلاگ مانند سایر زبان های توصیف سخت افزار به دو روش طراحی از بالا به پایین و طراحی از پایین به بالا شروع به مدل سازی مدارهای دیجیتال می نماید که روش اول کاربرد بیشتری دارد در این روش عناصر اصلی با استفاده از وریلاگ در بالای مدل سازی قرار گرفته و پارامترهای کم ارزش در پایین تر قرار میگیرد همچنین Verilog را میتوان زبان برنامهنویسی دانست که برای طراحی سختافزارهای دیجیتالی استفاده میشود. این زبان امکان توصیف سختافزارها را با استفاده از ماژولها و سیگنالهای دیجیتال فراهم میکند.

در یک تعریف کلی زبان وریلاگ یک زبان برنامهنویسی است که برای طراحی و شبیهسازی سیستمهای دیجیتال استفاده میشود. این زبان به طور گسترده در صنعت الکترونیک و طراحی مدارات مجتمع توسط دانشجویان و متخصصان الکترونیک استفاده میشود.استفاده از وریلاگ اهمیت زیادی در طراحی سیستمهای دیجیتال دارد به عبارتی میتوان طراحی تمام مدارهای منطقی و سیستم های دیجیتالی که بر روی سخت افزار و سیستم های رایانه ای صورت میگیرد را وابسته به این زبان شبیه سازی قدرتمند دانست. این زبان به طراحان و متخصصان حوزه سخت افزار اجازه میدهد تا مدارات خود را به صورت سطح بالا و سطح پایین توصیف کرده و سپس این مدارات را به صورت شبیهسازی و تحلیل کنند. یکی از ویژگی های برجسته ای verilog دارد آن است که تحلیل مناسب و درستی که در verilog انجام میشود زمینه ساز ساخت و تولید قطعات سیستم های دیجیتال به صورت انبوه خواهد شد. با استفاده از وریلاگ طراحان میتوانند مدارات خود را به صورت قابل فهم و قابل تعقیب توصیف کنند و به راحتی اشکالات و خطاهای ممکن را شناسایی کنند و بهبود بخشید. با توجه به اینکه امروزه بخشی عظیمی از مدارهای کامپیوتری را مدارهای مجتمع و آی سی ها تشکیل میدهند نیاز به استفاده از زبان طراحی و شبیه سازی با توجه به گستردگی و پیچیدگی میان اجزا و قطعات مختلف بیشتر احساس میشود. این زبان همچنین به طراحان اجازه میدهد تا به صورت خودکار تستهای مختلف را بر روی مدارات خود اجرا کنند و عملکرد آنها را بررسی کنند. زبان وریلاگ که بعنوان یک زبان برنامهنویسی است که برای طراحی و شبیهسازی سیستمهای دیجیتال استفاده میشود. به صورت گسترده ای در صنایع مختلف از جمله الکترونیک، ارتباطات، خودروسازی و استفاده میشود. Verilog به عنوان یک زبان توصیف سختافزار به عنوان ورودی برای ابزارهای طراحی مدارهای مجتمع و FPGA استفاده میشود.

استفاده از زبان Verilog در حوزه طراحی سخت افزار بسیار مهم است زیرا به طراحان سخت افزار امکان میدهد تا با استفاده از یک زبان برنامهنویسی، سخت افزارهای پیچیده را به صورت سریع و دقیق طراحی کنند. همچنین Verilog به طراحان امکان میدهد تا با استفاده از شبیهسازیهای مجازی، عملکرد سخت افزارهای طراحی شده را بررسی کنند و در صورت نیاز، آنها را بهبود دهند. یک زبان توصیف سخت افزار مانند Verilog بسیار شبیه محیط برنامه نویسی عمل میکند و دستورات را به صورت خط به خط از سخت افزار اجرا کرده و روی محیط آن اجرا میشود انجام پروژه وریلاگ منجر به ایجاد طرح های دیجیتالی خواهد شد که با قابلیتهای خود، یک سیستم دیجیتال را در طیف وسیعی از انتزاعات توصیف میکنند.همچنین دسترسی به ابزارهای طراحی به کمک رایانه را برای کمک به فرآیند ایجاد در این سطوح فراهم می کند.از جمله ویژگی های مهم وریلاگ میتوان به قابلیت طراحی ترانزیستورها را بالاترین سطح تا پایین تر سطح اشاره کرد به عبارتی وریلاگ زبان قابل فهم سخت افزار است یعنی سخت افزار برای برای برقراری ارتباط با سایر اجزا در واحد محاسبه و منطق نیاز به یک زبان توصیفی دارید که وریلاگ از بهترین آنها می باشد اکثر طراحی مدارات منطقی ابتدا در وریلاگ طراحی و نوشته میشود و سپس توسط اجزاری سخت افزاری تحلیل می باشد به زبان ساده تر امروزه بسیاری از طراحان زمان زیادی برای کشیدن شماتیک مدارات منطقی صرف نمیکند زبان های توصیف سخت افزاری مانند وریلاگ کمک میکند تا مدارهای بسیار پیچیده به ساده ترین شکل ممکت قابل پیاده سازی و طراحی باشد و این مهم ترین ویژگی وریلاگ می باشد.این زبان یکی مهم زبان های طراحی ترانزیستور ها می باشد.

متلب پروژه چه نوع پروژه های Verilog را میتواند انجام بدهد ؟

انجام پروژه دانشجویی Verilog

انجام پروژه طراحی با Verilog

انجام پروژه کلاسی Verilog

انجام تمرین Verilog

مراحل شبیه سازی در نرم افزار Verilog

1- طراحی مدار : در گام اول از شبیه سازی باید مدار موردنظر در Verilog که شامل تعریف ورودی ها، خروجی ها، ماژول ها و سایر اجزای مدار است طراحی شود.

2- نوشتن کد verilog : در گام دوم باید کد موردنظر در verilog نوشته و شبیه سازی لازم صورت گیرد.

3- تحلیل و اعتبار سنجی : در گام سوم باید کد verilog نوشته شده را مورد ارزیابی و تحلیل قرار داد.تا اطمینان حاصل شود که مدار به دستی کار میکند

4- سنتر مدار : در گام چهارم باید مدار شبیه سازی شده سنتز شود در این بخش فایل verilog به زبان های دیگر مانند VHDL تبدیل می شود تا بتواند در سخت افزار استفاده شود

5- پیاده سازی مدار : در گام آخر باید مدار به صورت فیزیکی پیاده سازی می شود. این شامل طراحی PCB، تولید و نصب قطعات و تست مدار است.

ضرورت استفاده از Verilog در طراحی سخت افزار

وریلاگ یکی از مهم ترین زبان توصیف ساختاری سیستم می باشد که به کمک آن میتوان تمامی مدل سازی های مختلف برای طراحی انواع ترانزیستورها در ابعاد کوچک و نانومتری را با وریلاگ طراحی کرد. استفاده از verilog در طراحی سختافزارهای دیجیتال اهمیت زیادی دارد. با استفاده از زبان verilog میتوان به صورت دقیق و سریع، سختافزارهای پیچیده را طراحی کرد و عملکرد آن را بررسی نمود . همچنین وریلاگ به عنوان یک زبان استاندارد در صنعت الکترونیک و سختافزار استفاده میشود و بسیاری از شرکتهای بزرگ در این زمینه از آن استفاده میکنند. لزوم استفاده از وریلاگ در برنامهنویسی سختافزار نیز به دلیل پیچیدگی و حجم بالای سختافزارهای دیجیتال است. با استفاده از وریلاگ ، میتوانید به صورت دقیق و سریع، کدهای سختافزار را بنویسید و با استفاده از شبیهسازی، آنها را تست کرد verilog برای توصیف از ابزارهای و برنامه های مختلف برای شبیه سازی استفاده میکند که مدلسیم از اصلی ترین آنها می باشد وریلاگ همچنین در فرآیند ساخت انواع قطعات کوچک استفاده میشود با استفاده از ویژگی های توصیفی وریلاگ و استفاده از زبان های برنامه نویسی مرتبط میتوان انواع مدارهای معماری را طراحی و پیاده سازی کرد.

بخش های مختلف Verilog

1- ماژول : ماژول به عنوان مهم ترین بخش از وریلاگ معرفی میشود که برای تعریف و طراحی سیستم های دیجیتالی استفاده میشود

2- پورت : از دیگر بخش های مهم در وریلاگ پورت می باشد که پورتها به عنوان رابط بین ماژولها و اجزای سیستم عمل میکنند

3- ورودی و خروجی : ورودی و خروجی ها در وریلاگ به سیگنال های دریافت کننده و ارسال کننده مورد استفاده قرار میگیرد و به ماژول کمک میکنند تا با سایر ماژولها و اجزای سیستم ارتباط برقرار کند

4- سیگنال : سیگنال ها در وریلاگ به عنوان متغیرهای داخلی ماژول عمل میکنند

5- عملگرها : عملگرها در وریلاگ به عنوان انجام دهنده عملیاتهای ریاضی در سیستمهای دیجیتال استفاده میشود

6- مسیرها : مسیرها در وریلاگ به عنوان ارتباط بین سیگنالها و پورتهای ماژول عمل میکند

لزوم استفاده از Verilog در صنایع مختلف

1- طراحی سیستم های دیجیتال : یکی از اصلی ترین صنایعی که ارتباط بسیار نزدیکی با وریلاگ دارد سیستم های دیجیتال می باشد در تمامی این نوع سیستم از زبان Verilog برای طراحی گیت های مختلف استفاده میشود.

2- طراحی مدارهای مجتمع : در این حوزه از زبان Verilog برای طراحی مدارهای مجتمع و پیاده سازی بردهای مجتمع که کاربرد فراوانی در سیستم های کامپیوتری دارد استفاده میشود.

3- طراحی سیستم های شبکه : از دیگر حوزه هایی که استفاده فراوان Verilog در آن مشهود سیستم های شبکه می باشد در تمامی این سیستم ها از بردهای Verilog برای انتقال هر چه سریعتر اطلاعات استفاده میشود.

4- طراحی سیستم های حسگر و کنترل: در این حوزه از verilog برای طراحی انواع بردها و مدارهای حسگر و همچنین کنترلی استفاده میشود.

5- طراحی سیستم های پردازش سیگنال : از دیگر حوزه ها و صنایعی که Verilog استفاده فراوان در آن دارد سیستم های پردازش سیگنال است در این سیستم از Verilog برای کاهش نویز ، افزایش کیفیت دامنه سیگنال استفاده میشود.

6- طراحی سیستم های رمزنگاری و امنیتی : از جدیدترین حوزه های مورد استفاده از Verilog سیستم های رمزنگاری و امنیتی می باشد در این سیستم ها از verilog برای پیاده سازی قطعات و اجزای امنیتی استفاده میشود

آشنایی با اجزا و قسمت های مختلف زبان Verilog

1- ماژولها: یک ماژول در Verilog معادل یک واحد سخت افزاری است که شامل ورودیها، خروجیها و رفتارهای مشخصی است. ماژولها به صورت سلسله مراتبی میتوانند تعریف شوند و برای طراحی سخت افزارهای پیچیده استفاده میشوند.

2- ورودیها و خروجیها: در verilog ، ورودیها و خروجیها با استفاده از کلمات کلیدی input و output تعریف میشوند. این ورودیها و خروجیها مقادیر داده شده را به ماژول ارسال و از آن خروجی تولید میکنند.

3- سیگنالها: در Verilog ، سیگنالها برای انتقال داده بین ماژولها و قطعات سخت افزاری استفاده میشوند. سیگنالها با استفاده از کلمه کلیدی wire یا reg تعریف میشوند.

4- عملگرها: verilog شامل عملگرهای مختلف برای انجام عملیات منطقی و حسابی بر روی دادهها است. عملگرهای منطقی شامل AND، OR، NOT و XOR هستند، در حالی که عملگرهای حسابی شامل +، -، * و / هستند.

5- دستورات کنترل جریان: verilog شامل دستورات کنترل جریان مانند if, else, case و for است که برای اجرای عملیات منطقی یا حسابی در زمان خاص استفاده میشوند.

6- پارامترها: در verilog ، پارامترها برای تعریف ثابتهای مقداردهی شده در طول زمان استفاده میشوند. این پارامترها با استفاده از کلمه کلیدی parameter تعریف میشوند.

7- تعداد دادگان: در verilog ، دادگان را معمولاً با استفاده از نوع دادگان bit, reg, integer, real تعریف میکنند.

8- کامنت ها: در verilog ، شما میتوانید با استفاده از کامنتها (// یا /* */) توضیحات و توضیحات در کد خود قرار دهید.

اهمیت و جایگاه استفاده از Verilog در توسعه سخت افزار

امروزه استفاده از زبان های توصیف سخت افزار بر کسی پوشیده نیست این زبان ها رابط میان سخت افزار و نرم افزار بوده و دستورات را به اجزای دیگر انتقال میدهند .Verilog همچنین یک زبان برنامهنویسی است که برای طراحی و شبیهسازی سختافزارها استفاده میشود. این زبان به خصوص در طراحی مدارهای مجتمع و سیستمهای دیجیتال استفاده میشود. از آنجایی که Verilog یک زبان قدرتمند برای طراحی سختافزارها است، به خصوص در حوزههای مهندسی برق و کامپیوتر، محبوبیت بالایی دارد. دانشجویان مهندسی برق و کامپیوتر، به خصوص در رشتههای مرتبط با طراحی سختافزار، اغلب با Verilog آشنا میشوند و از آن برای پروژهها و تحقیقات خود استفاده میکنند. این زبان به طراحان سختافزار امکان میدهد تا مدارات خود را به صورت مفهومی توصیف کنند و سپس به زبان ماشین تبدیل شوند. Verilog به طراحان امکان میدهد تا به سرعت و با کارآیی بالا مدارات خود را طراحی و شبیهسازی کنند، که این امر در فرآیند توسعه سختافزار بسیار اهمیت دارد. Verilog همچنین به طراحان امکان میدهد تا به راحتی تغییرات در مدارات خود اعمال کنند و به راحتی آنها را بهینهسازی کنند

وظایف کاربردی زبان Verilog

1- طراحی و شبیهسازی مدارهای مجتمع و سیستمهای دیجیتال از مهم ترین وظایف نرم افزار وریلاگ می باشد.

2- پیادهسازی مدارهای تراشهای و FPGA ها با استفاده از وریلاگ به راحتی انجام میشود.

3- طراحی و شبیهسازی سیستمهای دیجیتال پیچیده در زبان وریلاگ به صورت مفهومی و بسیار ساده انجام میشود.

4- توسعه و اعتبارسنجی IPهای مجتمع از دیگر وظایف زبان قدرتمند وریلاگ است.

5-انجام تستهای اعتبارسنجی بر روی مدارات دیجیتال از دیگر وظایف کاربردی در وریلاگ است.

6- طراحی و پیادهسازی سیستمهای رمزنگاری به سهولت در وریلاگ انجام میشود.

7- توسعه نرمافزارهای تعاملی با سختافزار از دیگر ویژگی های استفاده از وریلاگ می بااشد.

متلب پروژه در حوزه های زیر نیز میتواند مشاوره تخصصی به شما ارائه بدهد.(میتوانید مقالات زیر را مطالعه نمایید.)

اهمیت زبان Verilog در چیست ؟

با توجه به گسترش سیستم های کامپیوتری امروزه طراحی مدارهای دیجیتال از اهمیت خاصی پیدا کرده است در حال حاضر شاهد هستیم کوچکترین قطعات با استفاده سیستم های دیجیتال طراحی میشود طراحی این مدارها نیازمند نرم افزارها مربوطه می باشد که زبان وریلاگ یکی از برنامه های نام آشنا در این حوزه است یکی از ویژگی های Verilog داشتن محیط کاربری ساده برای کاربران است استفاده از زبان وریلاگ به دلیل سادگی نسبت به سایر نرم افزارهای مدار دیجیتال کاربرد بیشتری دارد با استفاده از این نرم افزار توسعه سخت افزار میتوانید سیستم های ساده مانند فلیپ فلاپ ، حافظه و پردازنده تا سیستم های پیچیده مانند میکروپرسسور را طراحی نمایید به طور معمول وریلاگ مدار را در سطوح سوئیج ، گیت ، انتقال داده و رفتاری مدل سازی می نماید.

کاربردهای Verilog

1- قابلیت طراحی و شبیهسازی سختافزارهای دیجیتالی

2- توانایی شبیه سازی تراشه های ASIC

3- توانایی و پیاده سازی شبیه سازی سیستم های ارتباطی

4- قابلیت طراحی و پیاده سازی سیستم های تحت کنترل

5- قابلیت طراحی و پیاده سای سیستم های پردازش تصویر و صوت

6- امکان شبیه سازی و مدلسازی سیستم های دیجتیالی

مراحل انجام پروژه Verilog

- ارسال پروژه های Verilog از طریق فرم ثبت سفارش و یا از طریق تلگرام، واتس آپ یا شماره پشتیبانی.

- بررسی دقیق و کارشناسی پروژه Verilog وسط مجریان گروه متلب پروژه.

- اعلام هزینه و قیمت پروژه Verilog براساس میزان بودجه پرداختی کاربر.

- موافقت با کمترین هزینه اعلام شده توسط مجری و پرداخت نصف هزینه.

- شروع پروژه توسط مجریان گروه متلب پروژه با توجه به زمان تعیین شده توسط کاربر.

- ارسال نتایج انجام کار به صورت عکس خروجی پس از پایان کار.

- اطمینان کاربر از انجام درست کار و پرداخت مابقی هزینه.

- ارسال پروژه Verilog توسط متلب پروژه و تعیین زمان پشتیبانی ۷۲ ساعته برای رفع اشکال.

- در صورت ذکر خواسته کاربر فیلم نیز از نحوه انجام کار ارسال خواهد شد.

سفارش پروژه Verilog با آموزش کامل

بسیاری از کاربران که به سایت متلب پروژه مراجعه می نمایند یک سوال اساسی در ذهن آنها وجود دارد که آیا سفارشی که من ثبت میکنم شامل گزارش می باشد ؟

موسسه متلب پروژه رسالت کاری خود را بر انجام پروژه Verilog با ارائه گزارش کامل قرار داده است و حالت آموزش محور را در پروژه های خود گنجانده است و طوری سفارش انجام میشود که کاربر به صورت کامل در روند انجام پروژه خود قرار بگیرد انگار خوده مشتری سفارش خود را انجام داده است.

ضمانت در پروژه Verilog به چه صورت است ؟

انجام پروژه در موسسه متلب پروژه با توجه به بهره گیری از اساتید ممتاز که تجربه و تخصص بالا در حوزه پروژه Verilog دارند قرار داده میشود به صورت تضمینی است و این تضمین کیفیت تا رضایت مندی کامل مشتری ادامه خواهد داشت.

زمان تحویل پروژه Verilog چگونه تعیین میشود ؟

زمان درست و به موقع تحویل پروژه یکی از خواسته های اصلی مشتریان است موسسه متلب پروژه با داشتن صدها کارشناس حرفه ای و مجرب زمان بندی دقیق و درستی از خواسته شما برآورد کرده و تمام تلاش خود را در تحویل به موقع پروژه Verilog خواهد کرد.

آیا امکان کنسل کردن پروژه Verilog وجود دارد ؟

امکان کنسل کردن پروژه پس از شروع به کار انجام پروژه Verilog منوط به موافقت با مجری انجام کار می باشد در صورت موافقت کارشناس انجام کار میتواند سفارش به صورت دو طرفه لغو شود.

امکان برقراری ارتباط مستقیم میان مشتری و مجری Verilog

در بسیاری از تماس هایی که با موسسه متلب پروژه برای ثبت سفارش گرفته میشود این سوال توسط مشتری پرسیده میشود که آیا میشود با مجری پروژه Verilog در ارتباط باشیم ؟ با توجه به تجربه چندین ساله متلب پروژه در برقراری ارتباط مستقیم امکان برقراری ارتباط مجری و مشتری وجود ندارد و فقط از طریق موسسه با مجری در ارتباط هستید در صورت برقراری ارتباط مستقیم دیگر سیستم پشتیبانی سایت متوجه انجام پروژه شما نخواهد بود

نحوه اعتماد در پروژه های Verilog به موسسه متلب پروژه

موسسه متلب پروژه یک کسب و کار آنلاین و دارای مجوز های لازم برای فعالیت در این حوزه می باشد و با داشتن نماد اعتماد الکترونیکی در پروژه دانشجویی Verilog توانسته است اعتماد شما عزیزان را جلب نماید.

زمان پشتبانی از پروژه های Verilog انجام شده :

زمان پشتیبانی از پروژه Verilog موسسه متلب پروژه 72 ساعت بعد تحویل پروژه می باشد و در این زمان مشتری میتواند به صورت کامل سفارش خود را بررسی کرده و در صورت داشتن ایراد مشکلات خود را ارسال کرده تا برای مجری انجام کار ارسال شود.

نحوه پیگیری سفارش ثبت شده Verilog

پس از ثبت سفارش کارشناسان متلب پروژه هم از طریق شماره های پشتیبانی و هم از طریق برقراری ارتباط با شبکه های اجتماعی امکان پیگیری سفارش را برای مشتریان خود فراهم کرده است

نحوه قیمت گذاری در پروژه Verilog به چه صورت می باشد ؟

یکی از سوالات مشتریان عزیز که با کارشناس متلب پروژه تماس میگیرند همین موضوع می باشد که هزینه انجام پروژه Verilog من چقدر می باشد ؟

متلب پروژه با راه اندازی سیستم مناقصه ای و استعلام قیمت از صدها مجری انجام کار کمترین قیمت را از سمت مجریان دریافت کرده و در اختیار مشتری قرار میدهد به همین دلیل قیمت پروژه Verilog در متلب پروژه کاملا عادلانه و منصفانه است.